|

|

|

Satellite Events > REMINDER Industrial Workshop on 1T-eDRAM

|

|

REMINDER Industrial Workshop on 1T-eDRAM |

|

|

After three years of research and development, REMINDER consortium will present to the Scientific and Industrial Community the main outcomes of the project:

|

||

April 4thConference Center Maison Minatec

|

Registration: free of charge

|

|

To register please only send an email to coordinator@reminder2020.eu |

Workshop Program (under construction) | ||||

|---|---|---|---|---|

| Time | Topic | Speaker | Summary | |

| 09:30 - 09:40 | Welcome & Introduction | Francisco Gamiz (University of Granada) | ||

| 09:40 - 10:00 | Embedded 1T-DRAM System-on-chip design | Andy Pickering (Surecore) | ||

| 10:00 - 10:20 | 1TDRAM operation in III-V devices | Carlos Navarro (UGR) | ||

| 10:20 - 10:45 | Coffee break | |||

| 10:45 - 11:15 | INVITED: Future trends in DRAMs | Dr Minsoo Yun (SK Hynix) | ||

| 11:15 - 11:35 | 1T-DRAM demonstration in 3D Si-nanowires | Joris Lacord (CEA-Leti) | ||

| 11:35 - 12:00 | 1T DRAM Memory cut Development & Flow in FD-SOI UTBB CMOS technologies | Philippe Galy (STMicroelectronics) | ||

| 12:00 - 12:10 | Conclusion and Perspective | Francisco Gamiz (University of Granada) | ||

| 12:10 - 14:00 | Lunch | |||

Second REMINDER Industrial Workshop of Embedded 1T-DRAM memories

Organizer: Prof. Francisco Gamiz, Universidad de Granada & REMINDER Project

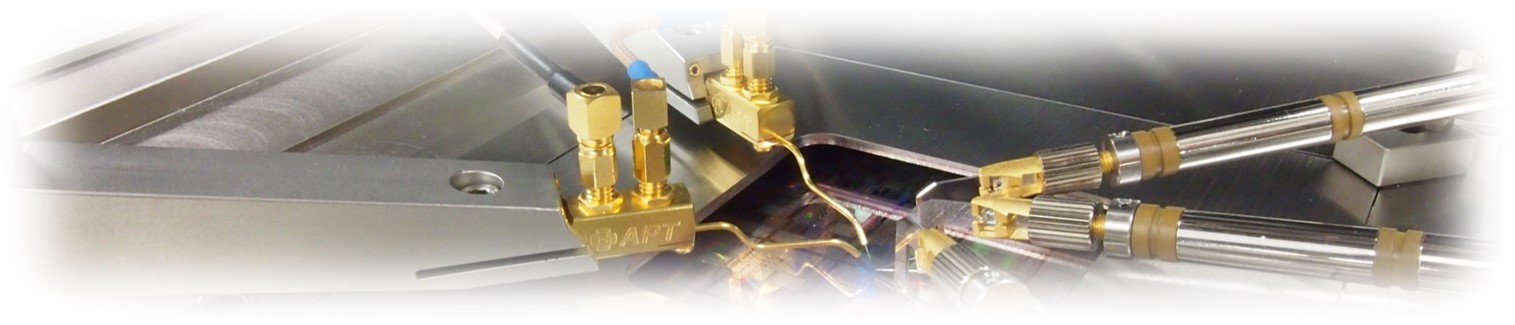

REMINDER is a Research and Innovation Action that has received funding from the European Union’s Horizon 2020 Research and Innovation. Launched in 2016, and with a duration of three years, REMINDER aimed to develop a quick lab-to-market embedded DRAM solution based on FDSOI technology and optimized for ultra-low-power consumption and variability immunity, specifically focused on Internet of Things cut-edge devices. After three years of deep research and development, REMINDER consortium will present to the Scientific and Industrial Community the main outcomes of the results. Memory demonstrators incorporating the 1T-DRAM memory solutions developed along the project will be presented. These 1T-DRAM memory solutions have been developed and fabricated using standard 28nm FDSOI technology. In addition, several approaches will be discussed including for the first time, the demonstration of 1T-DRAM memory cells in III-V semiconductors, and in 3D Silicon Nanowires technologies. |